2018年4月,在美國加州第二十四屆年度技術研討會上,臺積電首度對外界公布了創新的系統整合單芯片(SoIC)多芯片3D堆疊技術。若以臺積電2009年正式進軍封裝領域估算,SoIC是臺積電耗費十年才磨出的實現3D IC的高階封裝技術。

無獨有偶,日前,半導體IDM大廠英特爾也在上海召開了先進封裝技術解析會,詳細介紹了其在今年7月推出的一些列全新封裝技術架構的亮點和意義,其中就包括其在2018年12月舉行的“架構日”上宣布的3D封裝技術Foveros。

該舉動顯示,在制程和封裝領域,英特爾正以跨晶體管、封裝和芯片設計的協同優化快速革新。

為什么像英特爾、臺積電這樣的一直引領半導體產業制程技術發展的廠商都不約而同地把目光聚焦到先進的封裝測試技術上呢?

圖片來源:英特爾

圖片來源:英特爾

放緩的摩爾定律

自第一顆集成電路發明至今,集成電路相關產業已經走過了60年的發展歷史。在這60年中,半導體制程技術在摩爾定律的指引下,一路狂奔。

在過去摩爾定律的黃金時期,隨著制程的進化,同樣的芯片的制造成本會更低,因為單位面積晶體管數量提升導致相同的芯片所需要的面積縮小。所以制程發展速度如果過慢,則意味著芯片制作成本居高不下,導致利潤無法擴大。因此,摩爾定律背后的終極推動力其實是經濟因素。

不過,最近幾年隨著制程技術開始跨入10納米以下的極限領域,受制于工藝、制程和材料的瓶頸,摩爾定律開始呈現疲態。一味的追求先進制程并不能使廠商的經濟收益得到最大化。

所以,純晶圓代工的格芯和聯電已經先后宣布終止高端先進制程的研發,止步14納米,而英特爾在從14納米向10納米過渡的過程中也是幾經周折。

臺面上,目前還在繼續研究且有能力部署10納米以下高端先進的廠商只剩臺積電、三星、英特爾三家廠商。

不可否認的是,單純從制程技術上來看,雖有這幾家廠商勉力維持,但摩爾定律確實放緩了。

于是,如何讓芯片的性能繼續跟隨摩爾定律的腳步發展成為了集成電路業者開始探討的話題,而高端3D封裝就是其中一個新的選擇。由此,晶圓制造廠商的競爭也從明面上的制程之爭轉向先進封裝的“暗戰”,也就有了前述英特爾、臺積電等半導體大廠將目光瞄向3D先進封裝的事實。

新的突破口

3D封裝是在同一個封裝體內于垂直方向疊放兩個以上芯片的封裝技術,它起源于快閃存儲器(NOR/NAND)及SDRAM的疊層封裝,目前在NAND相關產品領域應用較為成熟。

3D封裝改善了芯片的許多性能,如尺寸、重量、速度、產量及耗能。

一般認為,3D封裝發展可能會經歷以下幾個階段:具有TSV和導電漿料的快閃存儲器晶圓疊層得快速發展;隨后會有表面凸點間距小至5μm的IC表面-表面鍵合出現;最后,硅上系統將會發展到存儲器、圖形和其它IC將與微處理器芯片相鍵合。

從發展趨勢來看,3D封裝為各類芯片的異質整合提供了可能,所以被認為是摩爾定律能夠延續的新的突破口。

圖片來源:英特爾

英特爾在此次解析會上強調其3D封裝技術在封裝過程中要達到低功耗、高帶寬、高性能三大要求。為此,英特爾全面布局了3大全新的封裝技術架構:

第一是Co-EMIB技術:基于2D封裝的EMIB和3D封裝的 Foveros,利用高密度的互連技術,實現高帶寬、低功耗,并實現有競爭力的 I/O 密度,全新的 Co-EMIB技術可連結更高的計算性能,能夠讓兩個或多個 Foveros 元件互連,基本達到單晶片性能。

第二是英特爾的互連技術ODI,提供封裝中小芯片之間,無論是芯片或模塊之間的水平通信或是垂直通信,互聯通信都有更多靈活性。

第三是MDIO:是基于先進介面匯流排 AIB( Advanced Interface Bus )發布的 MDIO 全新裸片間接口技術。MDIO 技術支持對小芯片 IP 模塊庫的模塊化系統設計,能夠提供更高能效,實現 AIB 技術兩倍以上的速度和帶寬密度。

這其中核心的部分是英特爾的Foveros技術,該技術通過在水平布置的芯片之上垂直安置更多面積更小、功能更簡單的小芯片來讓方案整體具備更完整的功能。

例如我們可以在CPU之上堆疊各類小型的IO控制芯片,從而制造出兼備計算與IO功能的產品;或者,我們可以干脆將芯片組(南橋)與各種Type-C、藍牙、WiFi等控制芯片堆疊在一起,制造出超高整合度的控制芯片。按照英特爾的規劃,未來基于Foveros的3D疊加和EMIB的2D疊加這些都在產品路線圖上。

有了堆疊方式和架構,英特爾Co-EMIB、ODI、MDIO等互聯技術就成為了3D堆疊、甚至3D/2D整合的過程中實現芯片互聯且保持靈活性的關鍵。

英特爾封裝技術路線圖,圖片來源:英特爾

英特爾封裝技術路線圖,圖片來源:英特爾

基于這些先進的封裝技術和架構,英特爾表示能夠為客戶提供各類低功耗、高帶寬、高性能的產品。

目前,英特爾第一個采用Foveros封裝技術的“ Lakefield ”處理器已經發布。

據介紹,Lakefield是一款針對移動PC的產品,基于英特爾最新的10nm工藝制造,采用Foveros 3D混合封裝,集成了一個大核心CPU和四個小核心CPU。

此外,Lakefield還集成了英特爾第11代的核顯,以及第11.5代IPU圖像處理單元,可以提供從圖像輸入到顯示設備端到端的數據流信號處理的全面支持。支持4×16-bit LPDDR4內存控制器以及多個I/O模塊。

Lakefield面向便攜式設備,雖有5個核心,但是整個芯片的大小還沒有一枚硬幣大,并且待機功耗僅有2mW,最大功耗才7W。高達3.1GHz的頻率也能夠讓其處理一些基礎的工作。

從參數來看,基于英特爾Foveros 3D封裝的Lakefield芯片確實能夠大幅提升性能降低功耗,這也算是為延續摩爾定律提供了新的方向。

英特爾的優勢

當然,客戶或消費者在購買技術或產品的時候不僅僅只是看性能而已。

事實上,半導體科技產業正在經歷非常快速的市場轉型,過去以硬件和終端為中心的商業模式正在加速向以數據為中心的智能互聯世界轉變。

隨著現代社會的數據量越來越龐大,英特爾也在圍繞這幾大挑戰發力,并且著手開發新的技術以及解決方案,以期能夠滿足新的商業模式的需求。

全新封裝架構和3D封裝技術的推出就是英特爾應對制程困境和新的商業環境的具體體現。

從技術層面來看,英特爾Foveros技術對于產業最大的優勢在于它可以將過去漫長的重新設計、測試、流片過程省去,直接將不同廠牌、不同IP、不同工藝的各種成熟方案封裝在一起,從而大幅降低成本并提升產品上市速度。同時,這種整合程度的提升也能夠進一步縮小整體方案的體積,為萬事萬物的智能化、物聯網化打開全新的大門。

與此同時,提供Co-EMIB、ODI、MDIO三大互聯技術則是英特爾相比其它3D封裝技術來說最大的不同,也是其優勢之一。

當然,英特爾最大優勢其實來自于其產業鏈的整合能力,在異構集成時代,IDM的模式讓英特爾的優勢顯化。

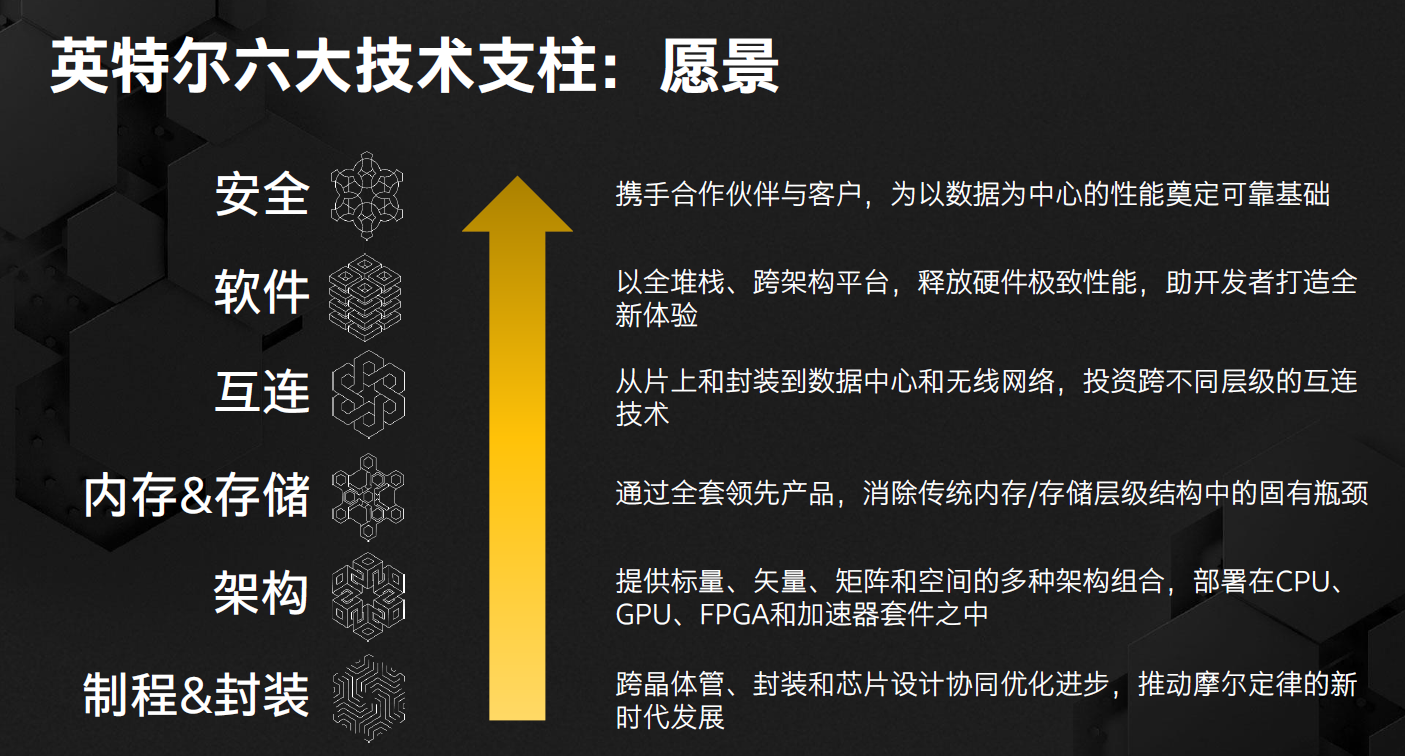

英特爾六大技術支柱,圖片來源:英特爾

這兩年,?英特爾在多個場合提出了制程和封裝、架構、內存和存儲、互連、安全、軟件為基礎的六大技術支柱戰略,以應對未來數據量的爆炸式增長、數據的多樣化以及處理方式的多樣性。

毫無疑問,封裝技術被英特爾放在了和制程同等重要的最基礎的位置,是其他五大支柱的支撐,也是英特爾參與市場競爭的核心優勢。