集成電路制造技術融合了半導體、材料、光學、精密儀器、自動控制等40多個工程科學技術領域的最新成就,代表當今世界微納制造的最高水平,其技術水平和產業規模已成為衡量一個國家信息產業競爭力和綜合國力的重要標志。集成電路產業處于電子信息產業鏈的上游,是一個有巨大市場規模且持續增長的行業,以2017年為例,集成電路產業對全球GDP的直接貢獻高達4086.91億美元。近年來,得益于物聯網、云計算、大數據、人工智能等領域的快速發展,集成電路的應用范圍正在不斷擴大。

與此同時,集成電路是電子信息產業的基礎和核心,一直在推動信息化和工業化深度融合中發揮著重要作用。比如,利用集成電路芯片對傳統機床進行智能改造,形成了數控機床的新興產業。汽車電子化是提高汽車安全性、舒適性和經濟性等性能的重要措施,引發了汽車工業的新革命。面向傳統行業定制的處理、控制、存儲相關集成電路,不僅將重構傳統行業發展生態,而且將驅動集成電路產業的發展。

國內外研究現狀

自1958年集成電路問世以來,以硅CMOS技術為基礎的集成電路一直遵循摩爾定律不斷向前發展,即集成電路上可容納的晶體管數量每隔18~24個月增加一倍,性能提升一倍,而價格保持不變。在CMOS工藝中,通常用特征尺寸來表征柵長,即溝道長度,通過縮小特征尺寸來提高芯片工作速度,增加集成度及降低成本。當前特征尺寸已經從1971年的10μm縮減到10nm左右,先進集成電路容納的晶體管數量已經超過10億個。

近年來,得益于制造技術的進步,相對于前一個技術節點,新技術節點的電路性能提升30%,功耗下降50%,面積縮減50%,可靠性基本保持不變。但是隨著集成電路工藝進入7nm技術節點(對應溝道長度約20nm),傳統邏輯和存儲器性能的繼續提升遇到技術瓶頸,集成電路發展正處于重大技術革新時期。未來5~10年,集成電路產業將沿著擴展摩爾(moreMoore)、超越摩爾(morethanMoore)和超越CMOS(beyondCMOS)三個技術路線向前發展。

(1)擴展摩爾。通過器件結構、溝道材料、集成工藝等方面的創新,微縮特征尺寸,繼續提升集成電路密度,相關技術路線已經規劃到近1nm技術節點,這正是本文討論的重點。

(2)超越摩爾。以價值優先和功能多樣化為目標,不強調特征尺寸的縮小,而是通過功能擴展及多功能集成,發展新功能器件與系統集成,實現應用層面的系統性能提高。

(3)超越CMOS。通過新材料、新結構、新原理器件的研發推動集成電路的發展,從物理工作機理與技術實現方式上突破傳統硅基CMOS場效應晶體管技術限制。

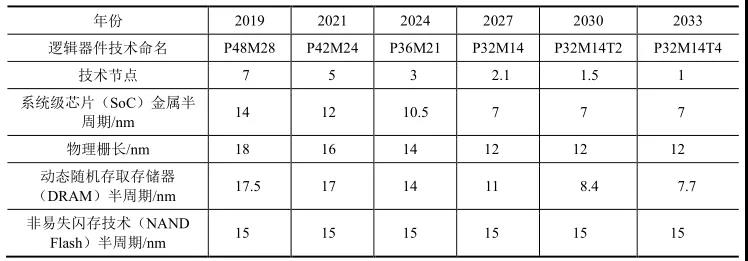

擴展摩爾技術路線是實現更小、更快、更廉價的邏輯與存儲器件的重要技術路徑。表1是電氣和電子工程師協會(IEEE)給出的國際器件與系統路線圖(internationalroadmapfordevicesandsystems,IRDS)。

表1IRDS2017版公布的邏輯器件工藝技術路線圖

短溝道效應是CMOS工藝技術向更小尺寸和更高集成度方向發展面臨的主要問題,當溝道長度縮小到納米量級時,即使不施加柵極電壓,也無法完全關斷MOS晶體管,源與漏之間會存在漏電流,使電路靜態功耗增大。為此,需要通過新工藝、新結構與新器件的不斷創新實現更先進的技術節點。

總體上來說,邏輯器件的發展呈三個重要趨勢:從結構上看,將由平面轉變為立體,三維晶體管技術(如FinFET等)成為主流器件技術;從材料上看,溝道構建材料將由硅轉變為非硅,非硅成為主流;從集成上看,類似平面NAND閃存向三維NAND閃存演進,未來的邏輯器件也會從二維集成技術走向三維堆棧工藝。從功耗和性能兩個維度來看,有兩條比較清晰的技術發展主線:采用新結構增加柵控能力,以實現更低的漏電流,降低器件功耗;采用新材料增加溝道的遷移率,以實現更高的導通電流和性能。

10nm及以下邏輯工藝將引入Ge/Ⅲ-Ⅴ族高遷移率溝道材料、GeSi源/漏應變材料等,結構上將采用納米場效應晶體管和隧穿場效應晶體管(TFET)等。而存儲器件,DRAM尺寸縮小到1x技術節點遇到工藝復雜、良率下降、成本上升、功耗增加等挑戰,DRAM在容量增加的同時刷新功耗增加,其容量擴展性遭遇巨大挑戰。

新興非易失存儲技術,特別是基于非電荷存儲機制的兩端器件,避免了電荷型MOS結構尺寸縮小過程中器件可靠性的嚴重退化問題,有望成為未來非易失存儲的主流技術。同時,三維集成是高密度存儲器發展的方向和核心技術。

近20年來,美國英特爾公司一直是邏輯集成電路技術發展的領頭羊,分別于90nm(2003年)、45nm(2007年)和22nm(2011年)技術節點上率先研發出晶體管溝道應變、高K金屬柵和三維FinFET技術,不斷推動著擴展摩爾技術的進步。

但是,隨著制造工藝復雜度和制造成本的不斷攀升,只有極少數集成電路廠商能夠承受7nm節點以下集成電路的研發費用。

目前,全球只有英特爾公司、三星公司、臺積電公司有能力研發7nm及以下集成電路技術。三星公司、臺積電公司于2016年年底領先研發成功10nm集成電路技術,2018年臺積電公司的7nm集成電路開始量產。中國中芯國際公司14nm工藝制程芯片2019年實現量產,并將于2021年正式出貨。

目前來看,考慮到技術復雜度的不斷增加和應用需求有所放緩,技術節點升級的周期將可能放緩至30個月以上。

待解決的關鍵技術問題

1nm集成電路對應的特征尺寸將達到7nm,硅集成電路技術在速度、功耗、集成度、可靠性等方面將受到一系列基本物理問題和工藝技術問題的限制,面臨的關鍵技術挑戰包括:①晶體管結構:如何重新定義底層設計;②溝道材料:如何獲取兼容CMOS工藝的高載流子遷移率材料;③極紫外投影光刻技術:如何提高分辨率和產率;④互連:如何開發新材料和新集成方法,以降低RC延遲時間;⑤設計與工藝聯合優化技術:如何尋找制造技術和設計電路圖形的關聯性。

1 晶體管結構

當集成電路進入22nm節點,傳統的平面場效應晶體管由于柵極不能完全控制溝道,從漏極到源極的亞閾值泄漏增大,無法進行進一步的縮微,被三維結構的FinFET取代。

FinFET結構類似魚后鰭的叉狀3D架構,由襯底上的硅體薄(垂直)翅片組成,通過在鰭片的三個面上施加柵極,可以有效控制溝道漏電流,降低溝道摻雜,提高載流子遷移率。高K金屬柵新材料、FinFET新器件結構和溝道倒摻雜新工藝的引入,可以降低工作電壓,減少器件與電路的功耗,這對于低功耗要求較為嚴格的消費類芯片尤為重要。

但是當集成電路進入3nm節點后,柵控與漏電問題將再次凸顯,再加上閾值平坦化和翅片上的熱耗散等難題,三柵FinFET不再適用,有可能被圍柵(gate-all-around,GAA)納米線器件取代。GAA在結構的四個面都施加一個柵極,從而保持溝道靜電完整性,實現更好的漏電流控制和載流子一維彈道輸運。

為了進一步克服物理縮放比例和性能限制,需要發展三維集成技術,形成類似3D-NAND閃存的垂直GAA結構,或者通過逐層堆疊的方法形成堆疊納米線晶體管,從而提高單位面積的電路集成度。盡管如此,對于未來的1nm集成電路制造技術,如何重新從底層設計具有超陡亞閾值斜率、超小亞閾值擺幅的低功耗器件結構,增強柵極控制能力,仍然是有待解決的難題。

2 溝道材料

當集成電路進入90nm節點后,集成電路產業界開始引入應變硅材料,并尋求更高載流子遷移率的新型溝道材料。在硅襯底上外延應變SiGe或Ge溝道可以提高空穴遷移率來增大驅動電流。

主要問題是需要嚴格控制外延層厚度和外延層與基底層之間的界面粗糙度。當應變層厚度超過臨界值時,應力弛豫會導致載流子能帶分布與波谷散射增加,從而造成遷移率退化。由于需要在前道工序中引入Ge,后續工藝需要防止Ge沾污和采用低工藝溫度。

Ⅲ-Ⅴ族化合物半導體,如銦鎵砷、砷化鎵和砷化銦等具有很高的載流子遷移率,與FinFET和GAA器件的集成在7nm節點集成電路表現出優異的性能,其挑戰在于和硅材料之間存在大的晶格失配,導致晶體管溝道的缺陷,尤其是在硅材料上生長銦鎵砷材料更為嚴重。當前利用選擇性外延技術集成Ⅲ-Ⅴ族化合物的研究正在進行中,其他技術如硅上鍵合技術也在探索之中。

為了有效避免短溝道效應,通常要求場效應晶體管溝道厚度小于溝道長度的1/3,1nm節點集成電路的溝道長度小于10nm,受量子效應限制,傳統三維半導體材料很難將溝道厚度減小至3nm以下。

具有原子層厚度的二維半導體材料具有比硅更小的介電常數、更大的帶隙和載流子有效質量。將這種新型材料應用于短溝道晶體管正在成為一個前沿探索方向。

1nm物理柵長的MoS2場效應晶體管已經被報道,其結構是以直徑1nm的單臂碳納米管作為柵電極,并以ZrO2包裹碳納米管形成背柵電容,以Ni作為源漏電極,晶體管亞閾值擺幅65Mv/dec,開關比106,漏致勢壘降低至290mV/V。但是載流子遷移率仍低于理論預期值,目前使用的微機械剝離等方法無法應用于集成電路生產。

3 極紫外投影光刻技術

光刻是集成電路制造中技術難度最大、成本最高的技術環節,成本占集成電路制造成本的35%以上,在每一代集成電路技術更新中都扮演著技術先導的角色。

透射式浸沒式193nm步進掃描投影光刻機的單次曝光分辨力理論極限為38nm,無法通過單次曝光形成22nm節點及以下集成電路關鍵圖層的目標圖形,需要采用多重光刻技術,即把原來一層光刻的圖形經過拆分之后放到兩個或多個掩模上,采用多次光刻共同形成一層關鍵圖層。通過四重圖形曝光手段,集成電路特征尺寸可以達到10nm。

通過八重圖形曝光手段,集成電路特征尺寸可以達到5nm。但是多重圖形曝光工藝復雜,如多塊掩模版、多次曝光、多次刻蝕、更為復雜的圖形布局拆分算法等,導致制造成本急劇上升。

為此,需要采用波長為13.5nm的反射式極紫外投影光刻技術,當前阿斯麥(ASML)公司商用的TWINSCANNXE:3400B極紫外投影光刻機數值孔徑已經達到0.33,5nm技術節點邏輯集成電路制造中金屬互聯層和高密度孔陣列均可以通過單次極紫外投影曝光完成。

未來5~10年,預計數值孔徑將提高到0.6以上,光源功率、掩模缺陷和光刻膠靈敏度三大關鍵技術將取得突破,結合離軸照明等分辨力增強技術,極紫外投影光刻單次曝光分辨力極限將逼近7nm,進一步采用多重圖形極紫外投影曝光技術,分辨力極限將達到2nm及以下,滿足1nm技術節點集成電路光刻需求。

4 互連技術

隨著互連線特征尺寸的不斷縮小、布線層數和長度的不斷增大,集成電路進入130nm節點以后,RC時間延遲逐漸成為阻礙時鐘頻率提高的主要因素。通常采用銅互連和低介電常數材料兩種方法來降低RC延遲時間。

相比于鋁及其合金互連,新一代的銅互連具有更低的電阻率、更高的熔點和更好的抗電遷移能力,可以降低RC時間延遲約40%,從而提高器件密度和時鐘頻率,并降低能耗。銅互連通常采用“大馬士革”結構的鑲嵌工藝,且被銅種子層、襯墊和薄擴散阻擋層所包圍。傳統的物理氣相沉積和擴散阻擋層的方法被原子層沉積方法所取代。

但是,當集成電路進入5nm以后,銅互連方案變得越發緊湊,將面臨銅線電阻過大、銅易擴散、低介電常數材料易擊穿等技術挑戰,光刻工藝造成的線邊緣粗糙度、趨膚效應、過孔錯位等因素也會使銅互連可靠性變差。延續傳統鑲嵌工藝的解決方案可能用鈷或釕取代銅進一步降低互連電阻。

其他集成制造工藝挑戰還包括均方根小于2nm的超低線邊緣粗糙度光刻工藝、小于2nm的擴散阻擋層沉積、無損傷化學機械拋光、無損傷化學清洗等。

5 設計與工藝聯合優化技術

當集成電路進入22nm節點及以下,工藝偏差和波動性相比特征尺寸所占比例日益增大,導致缺陷密度急劇上升,傳統的工藝和設計規則無法滿足產品性能需求,設計和工藝聯合優化技術(designtechnologyco-optimization,DTCO)成為必然的發展趨勢。

其基本思想是集成電路設計工程師與光刻工程師共同深入尋找制造技術和設計電路圖形的關聯性,既要滿足器件性能的要求,又能在芯片工廠內實現制造且具有足夠工藝窗口的技術方案,在集成電路生產之前就能有效評估可制造性,對晶體管架構設計、模塊級物理實現、材料和關鍵工藝技術,以及可靠性整個流程進行協同優化。

在設計層面,需要在明確的物理設計思路基礎上,對電路仿真進行進一步精確化設計,確定晶體管架構,如繞柵極納米線和納米板器件結構,仿真范圍從測試圖形擴展到整個標準單元。綜合考慮布線能力、功耗、時序和面積等因素,獲取精確的晶體管模型和庫架構,建立版圖分析和模型驗證方法,優化器件圖形設計規則,產生適于1nm技術節點的友好版圖,用于1nm技術節點光刻工藝和模型的輸入。

在制造層面,將晶體管架構、薄膜材料沉積、極紫外光刻和等離子體刻蝕等技術協同優化整合,實現復雜納米結構的高分辨率和高保真度。其中難度最大的是極紫外光刻協同優化,其流程涉及光源-掩模協同優化、光學鄰近效應修正、亞分辨率輔助圖形、高精度計量、光刻膠類型、光刻膠反應機理和隨機性效應、光刻后處理等,需要設計、工藝、材料和設備等各個領域的工程師緊密合作,以獲取合理的分辨率、工藝寬容度、焦深、掩模誤差因子和線條邊緣粗糙度等參數,并縮小標準庫單元區域的面積,降低器件結構和電學性能的偏差,滿足功耗、性能、面積、成本(power,performance,area,cost,PPAC)的目標需求。

優先發展技術領域

當前集成電路發展正處于重大技術革新時期,1nm技術節點的推進面臨兩大基本挑戰:一是由于晶體管物理性質限制,縮小特征尺寸越來越困難;二是制造工藝創新步伐放緩。這給我國的集成電路發展帶來了新的機遇和挑戰。建議優先考慮以下技術領域的發展。

(1)擴展摩爾技術。垂直GAA結構、堆疊納米線等晶體管架構,實現晶體管柵極長度的進一步微縮。異質材料體系的器件集成,突破多種物理失配限制,提高載流子遷移率。極紫外投影光刻設備及工藝,突破光源、掩模及檢測方法、光刻膠、多重曝光等技術,提高分辨率。高密度互連,形成新的互聯材料和圖案成形技術方案。設計與工藝聯合優化,實現精確的工藝波動性控制。

(2)超越摩爾技術。發展新功能器件與系統集成方法,通過硅通孔(TSV)三維集成技術將處理器、存儲器、傳感器、微機電系統、能源、生物芯片等整合成一個整體,實現新功能的應用。

(3)超越CMOS技術。新原理邏輯器件,包括隧穿場效應晶體管、負電容場效應晶體管、納機電邏輯器件和自旋電子器件等。新型存儲器件,包括自旋轉移力矩磁存儲、相變存儲器、阻變式存儲器及其大規模集成技術。憶阻器的神經仿生功能的研發,發展適用于憶阻器的類腦神經網絡計算處理機制和體系架構,開發類腦計算系統的計算模型及相關算法,以此實現大規模類腦神經網絡計算系統。

我國的發展戰略與對策建議

制定技術發展戰略時建議考慮如下問題。

(1)加強應用基礎研究,鼓勵原始創新,突出顛覆性技術創新。增加在新材料、新結構、新原理器件關鍵技術和基礎問題上的研發投入,為我國發展具有自主可控的集成電路產業提供新途徑。

(2)加強集成電路關鍵共性技術研發工作,聚焦圍柵納米線等新器件、極紫外光刻等新工藝研發,打通1nm集成電路關鍵工藝,為高端芯片在國內制造企業的生產提供重要支撐。

(3)從國家層面對集成電路制造技術體系和產業生態建設進行系統、科學地規劃和布局,遵循“一代設備,一代工藝,一代產品”的發展規律,加大集成電路關鍵材料、核心裝備、關鍵工藝和器件工程化的支持力度。

(4)積極推進微電子學科教育建設。針對集成電路制造技術多學科高度融合這一特點,加強具備綜合知識背景的集成電路人才培養,支撐我國新一代集成電路產業的重大跨越。

集成電路產業是支撐經濟社會發展和國家安全保障的戰略性、基礎性和先導性產業。當前集成電路發展正處于重大技術革新時期,擴展摩爾技術路線離1nm技術節點量產還有4至5代的發展空間。一方面,需要對新材料、新器件結構和新工藝技術進行創新研究,突破集成電路持續微縮的技術瓶頸;另一方面,需要發展系統集成新方法和新原理器件。

注:本文摘編自“技術預見2035:中國科技創新的未來”叢書《中國信息領域2030技術預見》一書第四章信息領域關鍵技術展望部分,內容有刪減。

封面圖片來源:拍信網